ご報告が遅れましたが、6月30日付で新卒の2003年から14年あまり勤務したNECを退職しました。

また、本日、東京法務局品川出張所においてヘテロDB株式会社の登記申請を行い、また、併せて新会社のチーフアーキテクト兼代表取締役社長に就任しました。

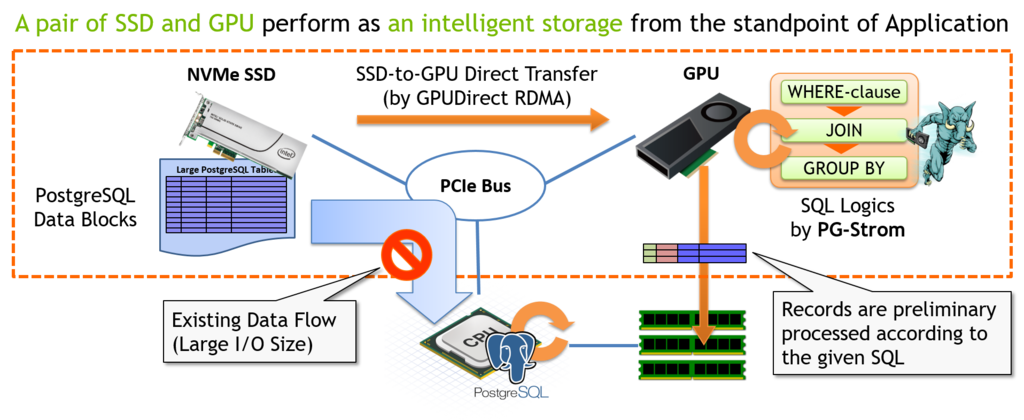

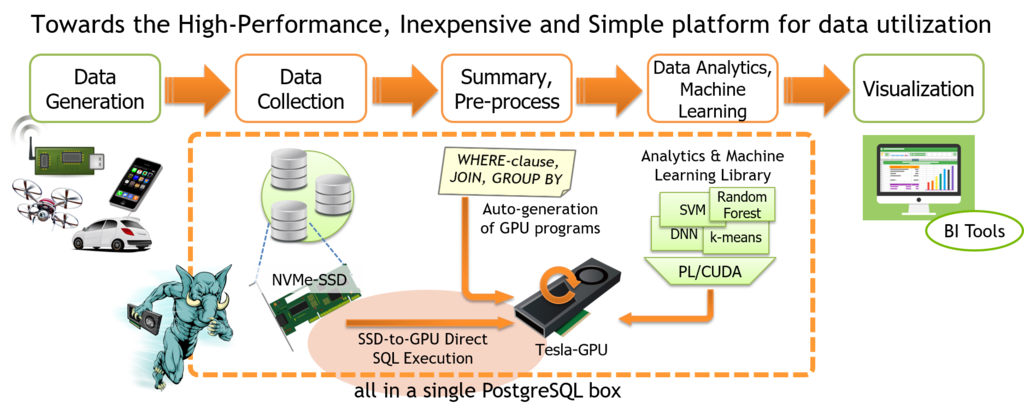

今後は、前職では実現できなかった、GPUやSSDなどヘテロジニアスな計算機資源を活用する事で、高性能、低価格、使いやすさを両立するデータベース製品の事業化を目指していく事になります。

どうぞよろしくお願いいたします。

web: http://heterodb.com/

10年以上も勤務した会社を辞めてスタートアップを立ち上げるというのは、おそらく人生の中でも上位に食い込むビッグイベントの一つだと思うので、今の決意や創業に至る一連の流れについて記録を残しておこうと思います。

(書き下してみたら意外と長かった!ごめんなさい)

オープンソースとの関わり

大学院を修了しNECに入社したのは2003年4月。

新人研修を経て配属されたのがHPC事業部配下で、今は亡きIA-64向けLinux kernelの開発とサポートを行う部隊。

大学の卒論で少しLinux kernelのデバイスドライバを書いた事があるとはいえ、本格的にLinux kernelのソースコードと格闘するのはこれが初めてで、HPC風味のパフォーマンスを重視するコーディングを徹底的に叩き込まれた。

一つキャリアの転機となったのは、当時リリース間近に控えていたLinux v2.6系の新技術調査という事で、全く偶然にSELinuxの担当となった事。

SELinuxの挙動を調べる中で、AVC(access vector cache)という極めて高い頻度で参照されるにも関わらず排他ロックで保護されている箇所が、HPC視点からはとても許容できないロック競合を引き起こしているように見えた。

IA-64 Linuxの製品では2004年時点でも既に32CPUのマシンがあり、『こんなロック競合を見過ごしたまま客先でSELinuxが使われたら大変なことになる!』と上司に相談し、当時、Linux kernelで使われ始めたばかりのRCU(Read Copy Update)によるSELinux AVCのロックレス化とコミュニティへの提案を行う事となった。

最終的にこの提案はLinux v2.6.9でマージされ、32CPU環境では修正の有無で1000倍以上の性能差が出るほどの顕著な改善となった。自分の中でコミュニティ指向が明確になったのは、この頃、NSAやRedHatやHPのエンジニアと議論を重ね、世界中で使われることになるソフトウェアの標準を自分が主導して作り上げたのだという経験が大きいと思う。

"好きな事"を仕事にするには?

ただ一方で、自分がSELinuxに関わり続けたいと思っても、事業会社である以上、例えば『Linux v2.6の新機能を調査する』という活動が終わってしまえば、少なくとも表向きは別の業務をこなしつつ、余った時間でSELinuxの活動をするしかなくなる。少なくとも肩身は狭い。

そういった経験から、自分の好きな事に時間を使うにはビジネスとしての裏付けを作らないとダメだという思いを固めつつあった。

幸い、当時のLinux推進センターでは、コミュニティに機能提案やパッチを投稿する事が推奨されており、(主業務は別にあるので100%コミットという訳にはいかないものの)手の空いた時間に開発するテーマを選択する事は比較的自由にできた。

2005年頃、jffs2ファイルシステムのxattr対応やbusyboxへのSELinux関連コマンドなど、組込み領域へのSELinux対応強化を行っていた。これは、製品出荷後長期間メンテナンスフリーで稼働せねばならない組込み機器の特性とSELinuxがマッチして付加価値に繋がるのではないかというアイデアが背景にあった。

また、2006年にはIPA未踏ソフトウェア創造事業に『SELinuxによるPostgreSQLのアクセス制御強化』のテーマで採択され、SE-PostgreSQLの原型を開発した。これも当時、セキュリティソリューションとしてのSELinuxの可能性を考えた時に『OSだけの制御では低レイヤすぎてお金を払うに値する利用シーンを考えられない』という声を多々頂いていたので、『じゃあ、上物のアプリケーションへ範囲を広げる。ビジネスの可能性は分からないので先ずは個人的に作る』という事で始めたものに、IPAがお金を出してくれたというもの。

Security Enhanced PostgreSQL - System-wide consistency in access cont…

その後、2009~2010年頃は『LAPP/SELinux』という事を言っていたと思う。これは、LAMPならぬLAPPスタックのセキュリティポリシーをSELinuxで一元管理しようという試みで、モチベーションは全く同じ。より上位のアプリケーションまで対応範囲を広げれば、SELinuxのビジネスとしての価値を見出せる領域を作り出せるのではないかというものである。

LAPP/SELinux - A secure web application stack using SE-PostgreSQL

ちょうど30才前後のこの頃、未踏でスーパークリエータの認定を頂いた事もあり、社内では割と自由に働かせてもらっていた。ただその一方でフラストレーションも溜まっており、『開発したものを早くビジネスにしなさい』と度々お小言を頂いていた一方で、どうすればビジネスにできるのか、上司も周囲も、誰も教えてくれなかったのである。

ただ、これは今だから分かるのは、SE-PostgreSQLのように新しいコンセプトで、まだ市場が存在するのかどうかも分からないような事業企画を、大組織の中で承認プロセスを通せる程度の隙の無さでビジネスプランを作成する方法なんて、上司にも分からなかったのではなかろうか。*1

私がやりたかった事とは?

端的に言えば技術は目的、ビジネスは手段とでもなるだろうか。

自分が楽しいと思う技術、手と頭を動かしたいと思えるソフトウェアを開発するために、自分とチームメンバーの人件費や開発費その他をペイできる程度のビジネスを作りたいという思いは一貫している。

ただ、それでユニコーン企業を目指すとか、世界を変革するために寝食を惜しんで事業を拡大するというのは少し違和感がある。やはり起点はテクノロジであり、面白い事、わくわくする事を(ニッチでもいいので)世の中で役立てたい。その結果として、ホームランかシングルヒットか、もしかしたら空振り三振かもしれないが。

一方で、まだ20代のこの頃は知る由もなかった事だが、NECでは何か新ビジネスを立ち上げる際、事業開始から3年後に数十億円レベルの売上が見込める事というのが一つの判断基準になっており、スモールビジネスというのはそもそも折り合いが悪かった。

この辺は他の大企業でも同様だと思うが、新しい技術を使ったソリューションを事業化するとして、また市場に受け入れられるのかどうかも分からない、ビジネスモデルは仮説段階、市場規模の推定も難しいような状況で、これだけの規模のビジネスを社員にコミットさせるというのは流石に無理筋であるとは思う。

新事業社内公募

2011年2月~2013年11月までNECヨーロッパに出向し、SAP社とのアライアンスを担当する事になった。

当時、サーバ製品の拡販のためSAP HANAの認証取得が重要な課題となっており、Linuxやデータベースに詳しく、外国人との折衝もこなせる人という事で白羽の矢が当たったと伝え聞いている。

これまでオープンソースに関わる仕事だけをやってきた自分にとって、ドイツでの3年間は、NECの顔としての立場で製品認証や保守スキームの折衝から契約交渉、プロプラ技術の検証、果ては機材の購買に至るまで、芸風を広げるのに大いに良い経験であった。

この時期、SAP社との協業の傍ら自分にとっては2つの大きなトピックがあり、これらが今後の方向性を決定づけた事になる。

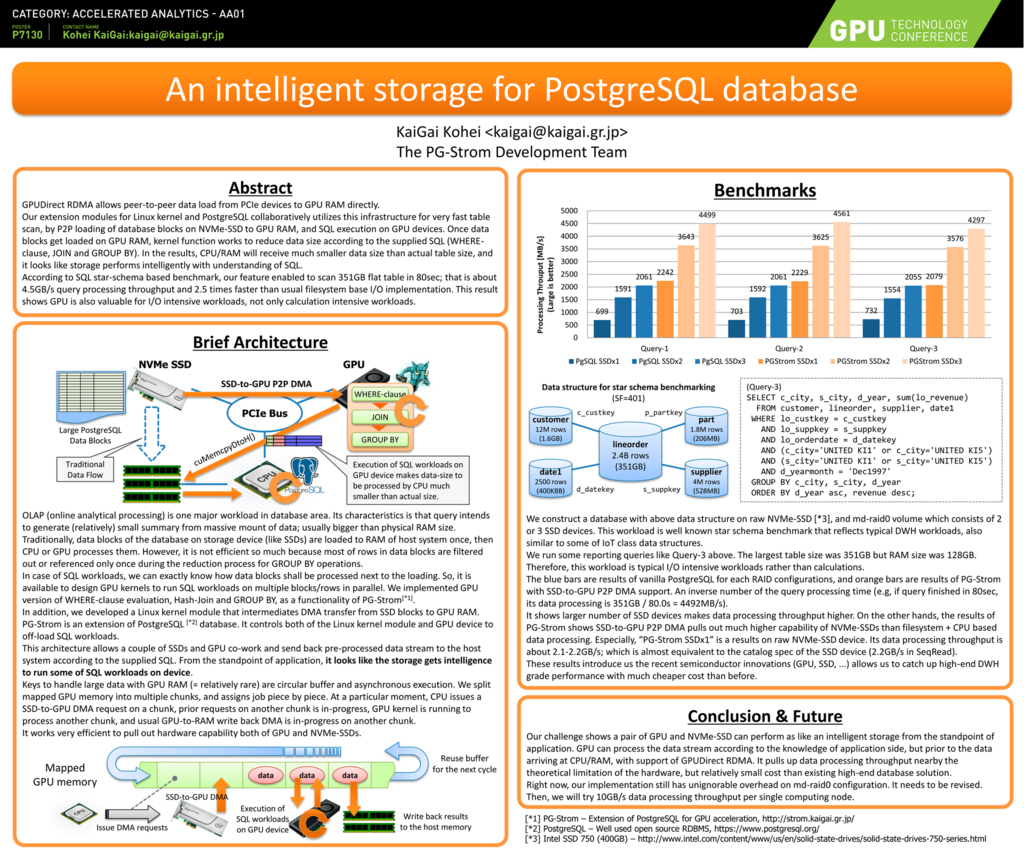

一つは、PGcon 2011でのTim Child氏のPG/OpenCLの発表に刺激を受けて勉強を始めたGPUによる並列処理。

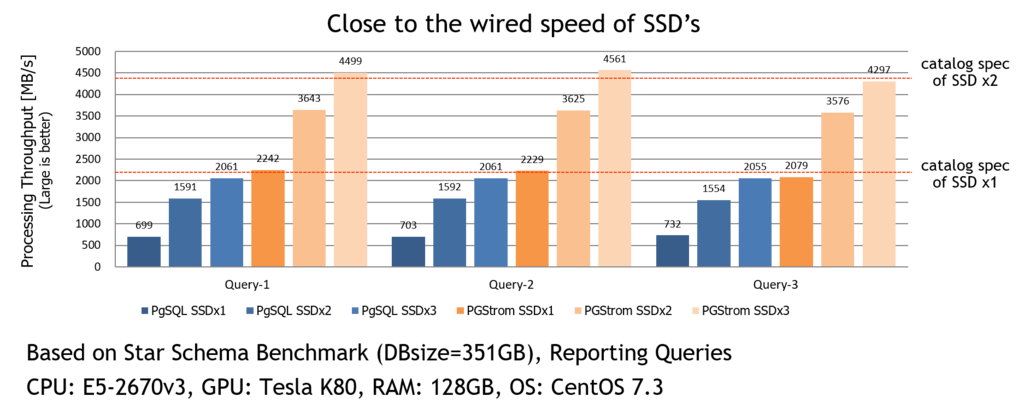

2012年の初頭にFDWベースで最初の実装を作ってみたところGPUの値段の割に性能改善効果が著しく、まさに"面白い!"技術であった。これがGPUによるデータベース高速化をメインの仕事にする出発点となった。また、この結果をブログにまとめたところ、同時期に中央研究所でGPUによるインメモリDBの研究を行っていた柏木の目にとまる事になる。後に彼はヘテロDB社の共同創業者となる。

もう一つは社内新事業公募。ドイツからの帰任後、また本業の仕事を抱えつつ"余った時間で"PostgreSQL関連のコミュニティ活動を行うという状況に嫌気が差していたので、実は帰国と同時にPostgreSQLの会社にでも転職しようと考えていた*2。

ただ、自分の手で開発した技術を軸にビジネスを作りたいという思いをまだ社内で真剣にぶつけてみた訳ではなかったので、一度くらい、社内新事業公募という形で会社のトップにぶつけてみて、それでダメなら辞めれば良いじゃないかという気持ちで、公募に誘ってくれた同期と、柏木、自分の3名で提案を書いてみた。

まぁ、S常務(当時)も社内ブログで『ダメなら会社辞めても事業を興すという気概のある社員の応募を求む』と吠えていた訳なので。

で、結果は応募110件中の2件で採択。辞めさせてもらえなかった。

PG-Stromプロジェクト

帰国後、PG-Stromを軸とする事業立ち上げを目指して、マーケティングとソフトウェア開発を並行して進める事となった。

この段階でのマーケティングとはつまり、この技術を事業化した時に本当に3年後〇〇億円の売上げを生み出せる可能性があるのかどうかを調べ、芽がないのであれば早々に投資を打ち切って無用な出血を抑えるという判断のために行うものである。

もちろん、技術の価値は顧客の課題解決手段としての価値とは異なるし、価値提案(VP: value proposition)の設定次第で、顧客にとってお金を払ってでも使いたい技術なのか、単なるwhat's newに過ぎないのかは変わってくる。当時、社内ではリーン・スタートアップが流行っており、仮説検証と称して、ユーザにVPをぶつけてその反応を伺いながら、提案シナリオや製品機能を修正するというアプローチを採っていた。

ただ、例えばWebサービスであればモックアップのWebサイトでサービスのコンセプトを議論するという事も可能であろうが、基盤ソフトウェアであるデータベース製品が『時々クラッシュします』では顧客にとっての価値を実証するどころでは無いわけで、まだソフトウェアがロクに動きもしない段階で、真っ先にマーケティング活動を始めて(そして、その分開発時間が割かれる事になる!)果たしてそれが正しいアプローチだったのかは今でも疑問が残る。

もちろん教科書的には、顧客にとっての価値シナリオとその時点での製品の完成度は別の概念だが、価値シナリオを納得するためには"実際に動くモノ"を見せるのが一番、百聞は一見に如かずで、ソフトウェアの完成度が未成熟な段階では確実に仮説検証の成功率は下がってしまうハズ。

結局、会社の方針もあり最初に米国市場でのユーザ開拓を行ってはみたものの『it's too early』という事でユーザとの仮説検証までは進む事ができず、自分たちの足で訪問でき、話を聞ける国内ユーザを対象にするよう方針転換する事となった。

退職、そしてヘテロDB社の創業

幸い、国内のユーザ様には何件か興味を持ってもらい、利用シナリオをあれこれ考えたり、ディスカッションを重ねる中で新機能の構想を具体化し、ようやく、技術と顧客にとっての価値が一本の線で繋がる実感は徐々に出てきた。

今になって思い返せば、8年前に『開発したものを早くビジネスにしなさい』とお小言を言われた時に、こういった活動をすれば(それなりに)根拠を持って話ができたんじゃなかろうか。

また、コンセプトや価値提案は様々な伝え方にはなるが、そのベースになるPG-Stromの機能や安定性が時間をかけて徐々に強化されてきたという事も、ユーザ様の納得感を得られる一助になっているだろう。

ただ一方で、少なくとも我々に見えている範囲では、NECの新事業のボリューム感として一桁以上小さい事は否めず、これはまだ2016年の段階でもまだ未解決の課題として残っていた。

しかも売上が年々縮小していく中、新領域に対する投資は非常に厳しくなっているため、2017年度からはマネジメント系の別業務をメインにした上で、PG-Stromはオープンソース活動として"空いた時間で"行わざるを得ないという事になった。

要は、新事業立ち上げを目的とした活動ではなく、空き時間のサイドジョブに戻ったわけで、いわば『10年前の振り出しに戻る』という事である。

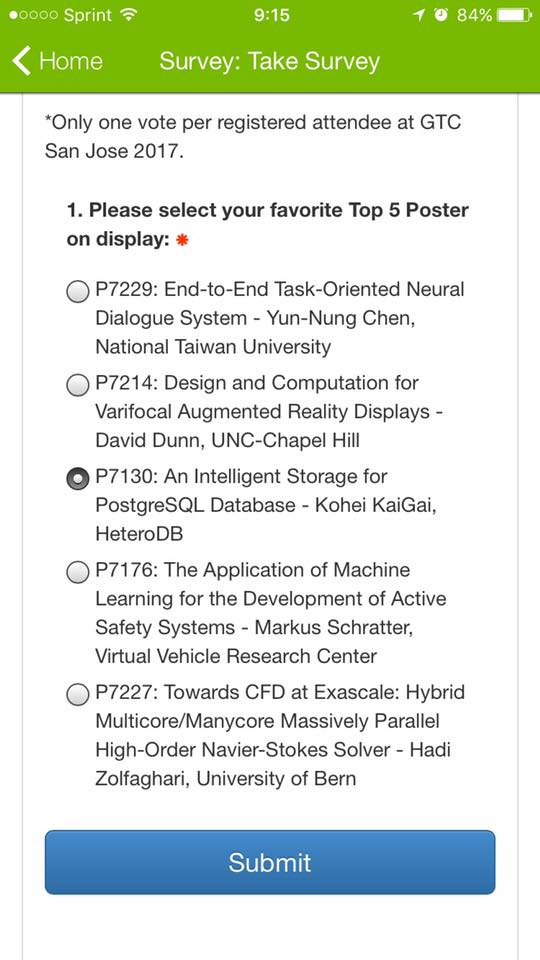

自分としては、大組織における壁を打ち破れなかったという事で忸怩たる思いがある一方、ユーザ様とのディスカッションや共同検証を経て、テクノロジーは確実に顧客課題を解決するソリューションに進化しつつあるという確信は持っている。

で、あれば、5年前に自分が作り出したソフトウェアが飼い殺しのような状況のまま、後発の競合が次々に先を行くのを指を咥えてただ眺めているという選択肢はあり得ない。そう考え、NECを出て自らPG-Stromを事業化するための新会社を立ち上げる事を決意した。

転職という選択肢はあったかもしれない。実際『PG-Stromの開発をそのまま継続していいのでウチに来てほしい』という誘いもあったが、投資予算の打ち切りをチラつかせながら、まだソフトウェアの機能・品質が未成熟な状態でマーケティング活動を行わざるを得なかった*3事を思い出すと、プロジェクトのガバナンスを現場から離れた人が握る事への不安はどうしても拭えなかった。

新会社でもやる事は基本的に同じ。PG-Stromをエンタープライズ領域で使える製品として世に出し、データベースという最も広範に利用されているソフトウェアの技術革新を通じて、GPUやSSDなどヘテロジニアスな計算機資源をユーザや社会の課題解決に役立て、ビジネスとして成り立たせていくために必要なあらゆる事をやっていく。

がんばるぞー